Industry's first multi-threaded multiprocessor IP core for embedded applications

### Baseline Specifications (Preliminary)

| Product                         | MIPS32® 1004K™ core |

|---------------------------------|---------------------|

| Process                         | TSMC 65GP           |

| Frequency (MHz)<br>(worst case) | >800                |

| Performance<br>DMIPS/MHz        | 1.5/core            |

| Total Area*                     | ~4.2mm <sup>2</sup> |

**Note:** Frequency, power consumption and size depend upon configuration options, synthesis, silicon vendor, process, and cell libraries

Quoted speeds are PTSI and don't contain OCV, clock jitter or design margin

\*Configuration: 2 cores, each core with 2 threads/core and 32KB Inst/Data caches, Coherence Manager (CM), and Global Interrupt Controller (GIC)

## **Key Applications**

#### Digital Home:

- Enhanced set-top boxes (STBs)

- HD digital consumer multimedia

- Residential gateways (RGWs)

Enterprise Communications Infrastructure

#### Network Attached Storage (NAS)

#### Office Automation/Multi-Function Products (MFPs)

• Medium/large office print/fax/scan

# MIPS32<sup>®</sup> 1004K<sup>™</sup>

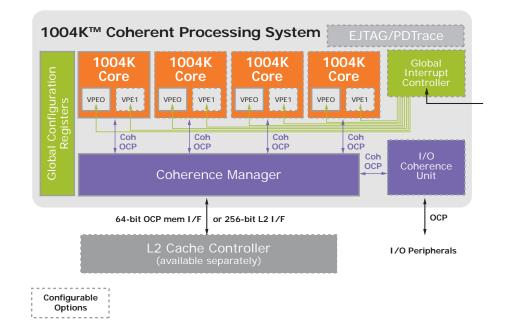

The MIPS32<sup>®</sup> 1004K<sup>™</sup> Coherent Processing System (CPS) is the next advance in licensable processing technology from MIPS Technologies. The 1004K CPS is a highly scalable multiprocessor platform that supports up to four cores connected via a coherent system architecture. Through the inclusion of hardware multi-threading in each core, the 1004K CPS is optimized to maximize performance in System-on-Chip (SoC) implementations and overcome historical performance limitations in embedded systems due to memory constraints and access latencies.

## MIPS32 1004K CPS Highlights

- A coherent multiprocessor system using multi-threading to extend performance beyond traditional multiprocessor solutions

- Up to four multi-threaded CPU cores, with two hardware threads/core

- Multi-threading complements multi-core leverages SMP operating systems and programming models, with minimal silicon cost adder

- Hardware I/O coherency offloads CPU software I/O coherency overhead

- Configuration and scalability at core and system levels, addressing a broad range of price/performance implementation points for optimal product implementations

- Licensable IP core enables broad industry adoption

## **Features**

#### A complete system for coherent multiprocessing, including:

- 1 to 4 1004K multi-threaded "base" cores (up to 8 hardware threads)

- Coherence Management (CM) unit the system "glue" for managing coherent operation between cores and I/O

- I/O Coherence Unit (IOCU) hardware block for offloading I/O coherence from software implementation on CPUs

- Global Interrupt Controller (GIC) system and inter-processor interrupt controller

- Extended 256-bit interface to L2 cache controller (available separately)

- EJTAG/PDtrace<sup>™</sup> block for advanced debug/trace of complete coherent system

#### 1004K Base Core

- 9-stage pipeline delivering more than 1.5 DMIPS/MHz per core

- Supports single- or dual-threaded operation per core

- Uses Virtual Processing Elements (VPEs) for hardware multi-threading

- Integer (1004Kc<sup>™</sup>) and floating point (1004Kf<sup>™</sup>) versions

- Support for Revision 1 of MIPS32 DSP ASE

- Coherency port has duplicate data cache tags for background coherency checks

- Design-time configurability for inclusion and sizing of instruction and data TLBs, caches, scratchpad RAM and other options

#### Floating Point Unit (FPU)

- IEEE 754-compliant FPU, compliant to MIPS<sup>®</sup> 64-bit FPU architecture (1004Kf version only)

- Supports single- and double-precision data types

- Separate in-order, dual-issue pipeline decoupled from integer pipeline

#### Coherency Management (CM) Unit

- Manages coherency using the MESI protocol

- Operates at same clock (1:1) as CPUs for maximum performance

- 256-bit extended interface for maximum throughput to (optional) L2 cache controller

- Supports performance enhancements via L1 cache-to-cache transfers, speculative reads to external memory, and globalized cache operations

- Global Configuration Registers (GCRs) for configuring/controlling CM scheme

#### I/O Coherence Unit (IOCU) – optional use

- · Bridges non-coherent I/O peripheral transfer and makes transactions coherent

- Supports per-transaction attributes for snooping L1 caches, L1+L2 caches, or noncoherent transactions, plus I/O prioritization

#### Global Interrupt Controller (GIC) - optional use

- Supports system-level interrupts; inter-processor interrupts

- Routes interrupts to particular core or VPE

- Configurable # of system interrupts (up to 256)

#### **Development Tools**

- MIPS Navigator<sup>™</sup> ICS IDE, software toolkit, MIPSsim<sup>™</sup>, EJTAG and PDtrace probes

- CodeSourcery SG++ toolchains for MIPS

Uses multi-threading to deliver maximum performance from each core

## Worldwide Offices

Headquarters MIPS Technologies, Inc. 955 East Arques Avenue Sunnyvale, CA 94085 United States Phone: 408-530-5000 Fax: 408-530-5150 www.mips.com info@mips.com

MIPS Technologies (Shanghai) Co., Ltd. Shanghai, China Phone: +86 21 6385 8383 Fax: +86 21 5306 0833

MIPS Technologies B.V. Jhubei, Taiwan Phone: +886 3 6583 561 Fax: +886 3 6583 563

MIPS Technologies B.V. Tokyo, Japan Phone: +81 3 5733 9541 Fax: +81 3 5733 9545

MIPS Technologies B.V. Remscheid, Germany Phone: +49 2191 900 200 Fax: +49 2191 900 208

MIPS Technologies B.V. Haifa, Israel Phone: +972 4 851 5080 Fax: +972 4 851 5090

© MIPS Technologies, Inc. 2009. All rights reserved. MIPS, MIPS32, MIPS16e, 24K, 24KE, 34K, 74Kc, 74Kc, 74Kf, 1004K, CoreXtend, and MIPS-Verified are trademarks or registered trademarks of MIPS Technologies, Inc. in the United States and other countries. All other trademarks referred to herein are the property of their respective owners. Printed in the USA. Rev 0509